Industry design challenges

As IoT systems evolve to meet advanced use cases, building a suitable System on Chip (SoC) becomes increasingly challenging. Integrating new features and pushing the performance envelope, all the while maintaining robust security and meeting power efficiency targets – designing an IoT SoC is more complex than ever.

The challenges faced by IoT SoC designers can be broadly classified into three main categories:

Slow SoC development cycle:

Time to market is a key concern for SoC designers. This means that slow design cycles can jeopardize a first mover advantage and the sooner a chip goes to production, the sooner a return on investment can be realized.

Difficulties designing a secure chip:

Security is a key priority for the SoC designers, particularly in IoT. Designing security into a modern, advanced SoC can be a substantial task and stakes are high – security oversights can become significant vulnerabilities down the line, putting reputation and revenues at risk.

Achieving ‘right-sized’ performance:

IoT devices span from sensors and industrial controllers up to gateways and smart cameras. Optimizing an SoC for a specific use case is key to differentiating an SoC, and by extension, the end product. As a result, there can be no ‘one size fits all’ solution.

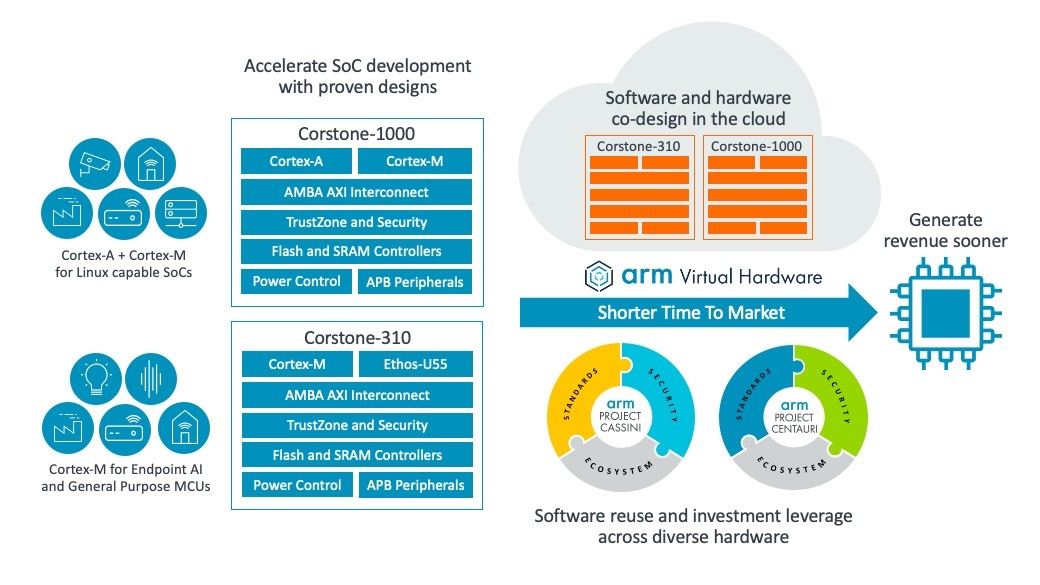

Launched last year, Arm Total Solutions for IoT, is a solutions-based approach to IoT design with three key pillars, including Arm Corstone. Today, we are announcing two new Arm Total Solutions:

Arm Total Solutions for Voice Recognition with Corstone-310 based on the fastest, and most secure Cortex-M processor ever, Arm Cortex-M85.

Arm Total Solutions for Cloud-native Edge Platform with Corstone-1000 for Linux capable design for cloud-native applications

Additional pillars of Arm Total Solutions are Arm Virtual Hardware, which is a virtual replica of the Corstone design in the cloud to enable modern software development and Project Centauri, an initiative to scale IoT innovation by enabling software reuse and leverage.

Arm Corstone is designed as the foundation for an efficient, high-performance SoC and includes a reference design to efficiently integrate Arm IPs with power, clock, debug, and security infrastructure. It provides the foundation for each Total Solution for IoT. Let us dive into these two new reference packages in more detail.

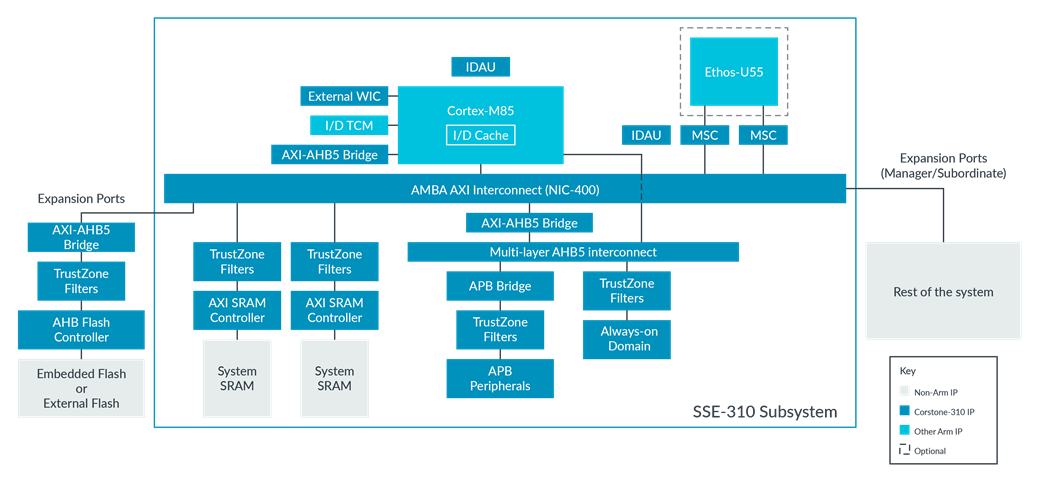

Corstone-310

Corstone-310 offers SoC designers a reference design with full modification rights to act as the foundation of secure, high-performance chips based on the Cortex-M85 CPU. Corstone-310 helps designers push MCU performance to new heights, combining the leading scalar and ML performance of Cortex-M85, with additional ML acceleration provided by the optional Ethos-U55 NPU. For more information on Cortex-M85, please read Introducing Cortex-M85.

With Cortex-M85, designers can now build MCUs with higher performance than ever to meet demanding applications such as object and voice recognition. Previously, the highest scalar performance available in the Cortex-M portfolio could be found in the Cortex-M7 processor, however this CPU did not have an associated reference design. With Cortex-M85, Corstone-310 has been built from the ground up to leverage the advanced capabilities of the CPU, making it easier than ever to build the highest performing MCUs.

Integrating processor IP effectively into a system can be difficult. With Corstone-310 this step has already been taken care of, offering Cortex-M85 fully integrated into a subsystem that has been architected by Arm for optimal performance and efficiency. A common challenge is building a power and clock control infrastructure that is capable of meeting stringent power targets for the use case. The subsystem included in Corstone-310 has pre-integrated power and clock domains for precise control over different aspects of the design.

Security is another key challenge for SoC designers. Cortex-M85 dramatically improves on its predecessor in this regard, with support for Arm TrustZone and PACBTI. However, extending this level of security to the rest of the system can pose an additional challenge. Architecting a complete security infrastructure can be a time-consuming task and one where mistakes can result in serious security vulnerabilities. The Corstone-310 subsystem has a pre-built TrustZone infrastructure – secure and non-secure code segregation is enforced across the entire system, including partitioning memories and designating peripherals as secure or non-secure.

Furthermore, Corstone-310 fulfils many of the requirements of TBSA-M, a specification of security best practices when designing systems around the Armv8-M architecture. TBSA-M forms part of the Arm Platform Security Architecture (PSA), and as a result Corstone-310 offers an excellent starting point for achieving PSA certification. Secure software design is also simplified thanks to a Trusted Firmware-M (TF-M) port, which implements the Secure Processing Environment for Armv8-M and Armv8.1-M architectures, paving the way for PSA Certification. Both PSA Certified and TF-M form part of the software pillar of Project Centauri, described in the following part of this blog post.

Corstone-310 integrates Arm’s latest high-performance IP in a secure and efficient manner. With the Corstone-310 Total Solution, SoC designers and software developers have the perfect starting point for building the latest generation of IoT devices. Learn more about Corstone-310.

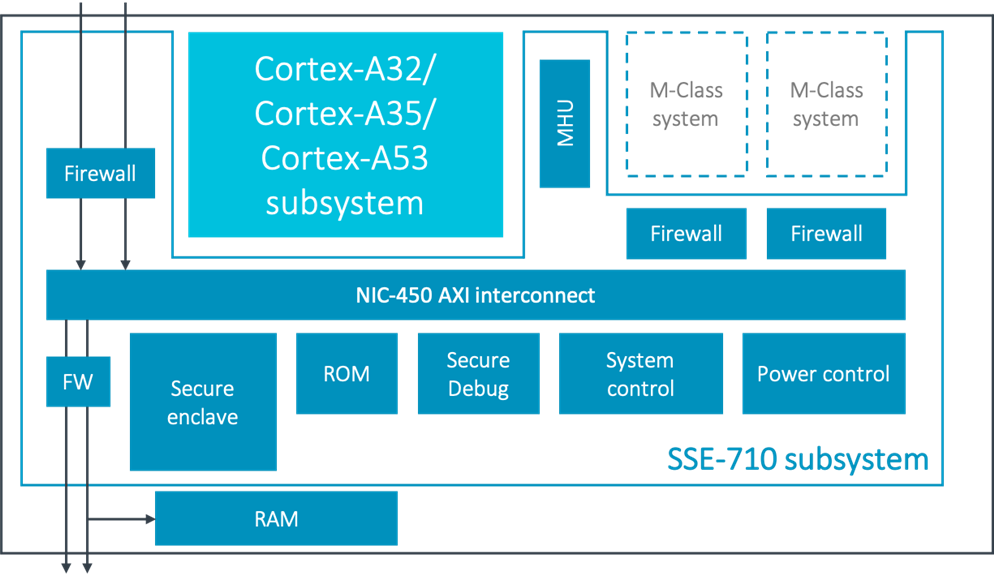

Corstone-1000

The IoT market requires not only MCU-based SoCs but also higher-performant processors capable of running major Linux distros “out-of-the-box”. The new Arm Total Solutions for IoT targeting A-class applications addresses this space and is based on Corstone-1000.

Corstone-1000 integrates the Arm Cortex-A and enables easy implementation of heterogeneous systems with Cortex-M processors, providing the best of both worlds: high performance and extreme power efficiency in a single system. The Cortex-A processor is scalable from Cortex-A32 to Cortex-A53, giving the options of implementing a diverse range of applications for example, smart wearables, gateways, and high-end smart cameras. Corstone-1000 comes with an extensive set of configuration options which have been fully verified. Learn more about Corstone-1000 [https://developer.arm.com/Processors/Corstone-1000].

Software reuse to help reduce even further time to market is facilitated by Corstone-1000 System Ready IR certification. Arm SystemReady IR is a hardware and firmware compliance certification program, enabling generic off-the-shelf operating systems to work out of the box so that a one-time effort becomes scalable. Learn more about Arm System Ready.

Corstone-1000 comes with two prototyping platforms to enable early software prototyping. A Fixed Virtual Platform (FVP) and an FPGA-based. Both platforms are supported by an open-source reference software stack.

Security has been fully integrated from the very definition of Corstone-1000. The Secure Enclave (SE) is an essential component to it. It uses Cortex-M0+ processor that is included in Corstone-1000. With separate system resources and a separate OS, the SE acts as a secure environment in which to store secrets and process sensitive information. A Cortex-M0+ in the SE is the Root-of-trust (RoT) for the SoC. The open-source software stack is composed of two boot loading stages on the Cortex-M0+, based on mcuboot, and TF-M as run time software. The host Cortex-A is brought out of rest by the SE. Corstone-1000 is PSA level 2 ready certified thanks to its SE.

Arm Virtual Hardware for Corstone-310 and Corstone-1000

Arm Virtual Hardware (AVH) is an evolution of Arm’s robust modelling technology, providing functionally accurate models of Arm-based SoCs in the cloud. Corstone-310 and Corstone-1000 are now available as AVH Corstone models so developers can immediately get up and running on these brand-new platforms.

With AVH, software development can start well ahead of hardware availability, allowing for co-development of hardware and software. AVH allows developers to take advantage of modern CI flows, and offers massive scalability, removing the need for large board farms. The net result is a dramatic improvement in time to market, as software and hardware development can run in parallel, the software runs faster, and testing can be scaled across large instances.

More information on AVH.

Project Cassini and Project Centauri

Project Cassini and Project Centauri are software initiatives which support developers of Cortex-A and Cortex-M designs respectively. They share the three pillars of standards, security and, ecosystem.

Standards:

Common development standards help to drive the industry towards code-reuse. This includes the SystemReady program for Linux capable SoCs and the Open-CMSIS software components for MCUs.

Security:

The security pillar covers PSA Certified, a framework for building secure connected devices, and Trusted Firmware-M, the implementation of the secure processing environment for Armv8-M and Armv8.1-M.

Ecosystem:

Enabling developers through collaboration with key partners on platform software and middleware, tooling, and ML capabilities across the entire IoT ecosystem.

Cassini and Centauri help to drive the Arm-based MCU and Linux ecosystems towards a world of standardized and reusable software by establishing development best practices and supporting the designers of applications based on Arm Corstone.

More information on Centauri.

Summary

IoT hardware and software development is more complex than ever, driven by increasingly demanding use cases. Arm Total Solutions for IoT provides a holistic answer to the challenges inherent in building IoT systems, with Arm Corstone subsystems as their foundation. The Corstone-310 and Corstone-1000 enable new MCUs pushing the performance envelope and heterogenous Linux based systems for edge devices.

Get started with Arm Total Solutions